archy13 - stock.adobe.com

Seagate, Western Digital outline progress on RISC-V designs

Seagate and Western Digital provide updates on their RISC-V-enabled processor designs that can drive advances in data storage and security at the network's edge.

Storage drive rivals Seagate Technology and Western Digital this week outlined the progress they've made in designing specialized RISC-V processors to fuel advances in storing and securing data at the network's edge.

Seagate unveiled its first two processors based on the free and open RISC-V instruction set architecture. One is a high-performance core built with RISC-V-enabled silicon that Seagate said is functional in hard disk drives (HDDs) in the lab. The other is an area-optimized, low-power core for auxiliary or background workloads. Seagate declined to provide a timeline for when its RISC-V-enabled technology will ship in HDD products.

Also at this week's virtual RISC-V Summit, Western Digital showed off a flash controller and prototype solid-state drive (SSD) board that use its open source RISC-V-enabled SweRV cores. The company did not disclose product plans, but it is a long-time RISC-V proponent. Western Digital announced in 2017 that it planned to transition more than one billon cores per year to RISC-V to drive momentum of open source processors for data center and edge computing.

"RISC-V is an open standard, and using it in HDDs can provide advanced processing technology at little extra cost to the HDD company -- and, thus, to the end user," said Tom Coughlin, president of Coughlin Associates. He noted that practical uses are starting to emerge for RISC-V from storage to AI.

RISC-V advantages

The freely available RISC-V instruction set architecture holds appeal beyond storage. But one of the main attractions for Western Digital and Seagate is that they can customize the core design to suit their needs rather than making a general-purpose processor, such as ARM, fit for storage applications.

They envision the RISC-V benefits also trickling down to IT organizations in the form of lower latency, power savings, higher drive capacities at a faster pace, computational capabilities in storage drives, and improved security for data created at the edge of the network.

Richard Bohn, director of RISC-V core development at Seagate, noted that HDD capacity is expected to hit 50 TB by 2026. He said that level of density would require sophisticated algorithms to enable a drive head to hit a spot on the disk that is 30,000 times smaller than the width of a strand of human hair. Those motion-control positioning algorithms will require massive computation, and Seagate is using the RISC-V instruction set to address the computational challenge, he said.

Seagate also plans to leverage RISC-V cores to build computational storage HDDs that can process data at the drive level, rather than moving it to application servers, to reduce network traffic and I/O bottlenecks. Flash-based computational SSDs are already in the market, and Seagate's proposed new drives could give users a potentially cheaper computational HDD option. Seagate did not provide a timetable for its computational HDDs. Computational storage drives can be useful for analytics, AI and machine learning workloads that rely on data from edge devices.

Bolstering edge security

Securing data at the edge is another area of focus for Seagate with its RISC-V work. Bohn cited a potential use case of customers that install security cameras for surveillance. If a camera captures an individual committing a crime, the customer would need to prove the streaming video that lands on the storage devices is trustworthy and not an AI-generated deepfake, he said.

"That's one of the things that RISC-V can really help with," Bohn said. "By having a unified security infrastructure, where we've got the same security technology inside our disk drives [and] the same security technology inside endpoint devices like video cameras, we're able to create authentic data transfers through the storage ecosystem to bring some of that security to the edge."

During a RISC-V Summit keynote, Seagate CTO John Morris said the company created a prototype of a trusted endpoint using a field-programmable gate array (FPGA) development board and tapped Keystone enclave technology to bind all security-sensitive services. Keystone is an open source framework for building trusted execution environments based on the RISC-V architecture. Morris said Seagate is also pursuing other open source technologies for trusted hardware, including OpenTitan, a reference design for silicon root of trust chips.

Seagate began its work with RISC-V in 2015. Cecil Macgregor, the company's vice president of application-specific integrated circuit (ASIC), said Seagate is initially applying RISC-V to HDDs but plans to use it in other areas in the future. One option under consideration is rack-scale systems, he said.

Western Digital's expansive RISC vision

Western Digital focused on its flash storage controller and SSD board at this week's RISC-V Summit. But during a keynote at the virtual event, Siva Sivaram, the company's president of technology and strategy, outlined a sweeping RISC-V vision that spans products, the processor cores that go into the products, and an open data-centric architecture to integrate the products.

"Having a company of that size transition their entire product portfolio to RISC-V is going to be a very big deal," said James Sanders, an analyst at 451 Research, which is part of S&P Global Market Intelligence. "Western Digital stands to save a decent amount of money on ARM licensing. But this isn't going to be the death knell to ARM by any stretch of the imagination. RISC-V has a lot of ways to go to be more mature for other applications."

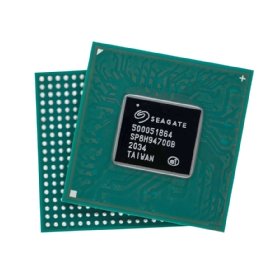

Updating WD's progress on the product front, Sivaram said RISC-V would be "the driver for the controllers that go into all of our products," whether client, mobile, consumer or network-attached devices such as HDDs and SSDs. He displayed a photograph of a Western Digital SSD controller, with a SweRV core inside it, and described it as "our prototype for getting this product into the market."

On the core front, Sivaram noted the company's release of its first RISC-enabled SweRV EH1 core for internal use in early 2019, and later, through CHIPS Alliance's GitHub site. Sivaram claimed several semiconductor organizations have started using the open source core, and recently, a large GPU company downloaded it.

Western Digital also released a dual-threaded, high-performance embedded SweRV EH2 core and a low-power, moderate-performance SweRV EL2 core customized for sequencer and state machine IP functions. Sivaram claimed the cores compare well to alternatives in performance benchmark tests, and equally importantly, reduce power consumption.

Updating his company's efforts to create new data-center architectures, Sivaram spotlighted the open source OmniXtend memory fabric that Western Digital released last year built to address the bottleneck at the processor. He said the OmniXtend hardware design is now available through the open source community, but he said it's only a start.

"The OmniXtend can act as a fabric, but a true open coherency bus has to be developed for RISC-V," Sivaram said. He urged the community to "take this as a call to action."