Server hardware guide: Architecture, products and management

Today's server platforms offer various options for SMBs and enterprise IT buyers; it's important to learn the essentials before making any purchasing decisions.

The explosive growth of cloud computing platforms and the preceding wave of virtualization have significantly altered the role of the server among SMBs and enterprises.

Virtualization enabled organizations to load multiple virtual machines (VMs) on a single physical box, boosting hardware utilization and offering the ability to consolidate IT resources. Virtualization paved the way to the cloud, as IT managers could transfer VMs off-site to run on hyperscale providers, such as AWS, Google and Microsoft. Business-critical applications -- such as CRM, HR and ERP -- previously operating on in-house servers, also journeyed to the cloud in the form of SaaS.

That said, businesses of all sizes will continue to own and operate servers. Some organizations prefer to maintain in-house servers and private clouds for particularly sensitive workloads or applications that are too costly or difficult to migrate to a public cloud platform.

Read on to learn more about the different types of servers, their evolving architectures and what IT buyers should look for regarding key requirements.

Types of server hardware

The mainframes of the 1950s and 1960s can be considered the original servers, but the history of servers in the modern sense starts in the 1980s with the invention of x86 servers running OSes, such as Novell NetWare or Banyan Vines. Today, servers come in a range of form factors and offer varying capabilities, finding a home in small businesses, large enterprises and everything in between.

The following is a rundown of some of the prevalent types of server hardware:

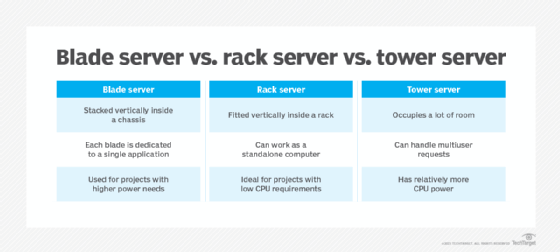

- Tower servers. A tower server resides in an upright, standalone case, resembling a tower-style PC. These servers provide the benefit of easier cooling because they offer a relatively low component density. They are also comparatively inexpensive, making them an option for smaller businesses on a limited budget. Many small businesses favor tower servers because they do not require a rack, making them relatively easy to deploy. However, tower servers take up more space than other server types.

- Rack servers. A rack server is designed to be mounted on a server rack in a data center. Rack servers often play an all-around computing role in the data center, supporting a multitude of workloads. These servers take up less space than a tower server. Rack servers and server racks are built to consistent size standards so that servers from multiple vendors can be stacked together. Standardization also makes adding new servers or replacing old ones a straightforward task for engineers. Cable management, however, can prove a challenge when maintaining rack servers, which are tethered to power supplies, networking equipment and storage devices. Additionally, rack servers can be loud due to their high-speed fans and close proximity to one another.

- Blade servers. A blade server is a compact server designed to fit into a blade chassis. Blade chassis are designed to accommodate multiple blade servers, each dedicated to running a specific application. The chassis provides power, cooling and networking to the individual blades. Blade servers are a great option for those who require high-density computing. However, their specialized infrastructure and high initial cost make them less attractive to smaller businesses.

Blade servers offer greater processing density than other server types, providing a potential price and performance advantage. Blade server systems are simpler to repair than rack servers due to their hot-swappable, modular components. On the downside, blade servers have historically been built on proprietary architectures, making vendor lock-in a possible pitfall for buyers.

- Hyperconverged infrastructure. HCI systems aim to provide a simpler alternative to traditional IT infrastructure, combining compute, storage and networking technology in an integrated system. With a typical hyperconvergence offering, a midlevel data center engineer should be able to complete the tasks of initial hardware configuration, hypervisor deployment and software-defined storage implementation in about an hour. Vendors' products offer setup wizards to simplify the initial deployment process.

- Mainframes. The rise of client-server architectures in the 1990s was forecast to obliterate mainframes, but those high-end servers continue to exist. Today's mainframes offer the ability to support large volumes of simultaneous transactions and heavy I/O loads without taking a performance hit. Financial services firms conducting concurrent, real-time transactions are among the typical mainframe customers. The primary drawbacks to mainframes are their size, price tag and the specialized skill set they require.

Server hardware architecture

Like a PC, the key components of server hardware architecture include the motherboard, processor, RAM and storage.

The motherboard resides at the heart of the server, providing the central nexus through which system components are interconnected and external devices are attached. Advanced Technology Extended (ATX) is for tower servers or entry-level servers; extended ATX, or EATX, is often used in midlevel servers. Rackmount and enterprise-grade servers often use Server System Infrastructure Compact Electronics Bay or Enterprise Electronics Bay motherboards.

The processor, or central processing unit (CPU), resides on the motherboard. CPU components include the arithmetic logic unit, floating point unit, registers and cache memory. A server might also contain one or more graphics processing units (GPUs), which can support applications such as machine learning and simulations. Tensor processing units and neural processing units offer additional levels of processor specialization.

RAM modules also plug into the motherboard, serving as the system's main memory. RAM holds the OS, applications and in-use data for fast access by the processor. As for storage, a server might use a hard disk drive (HDD), a solid-state drive (SSD) or a mixture of the two.

A server's form factor influences its role. An enterprise data center, for example, will usually choose rackmount servers because they take up less space, enabling higher-density deployments.

An organization seeking to run a heterogeneous data center might choose rack servers for a different reason. Rack servers adhere to standard form factors, meaning multiple vendors' products can be installed within a rack. They also offer a range of power connections and network cabling choices. Large rack servers enable extensibility, accommodating additional processors, memory and local storage disks.

Blade servers, meanwhile, are geared toward single-vendor IT settings that seek to unite compute, storage and networking within a single system. This approach offers the benefits of faster deployment and simplified management.

Other trends in server architecture include disaggregation and composable infrastructure, which can be viewed as a continuation of converged infrastructure. Composable infrastructure uses software-defined methods to logically pool computer, storage and network fabric resources in a data center. Those resources become the basis for shared services, which admins can draw upon to compose compute instances on the fly.

Requirements

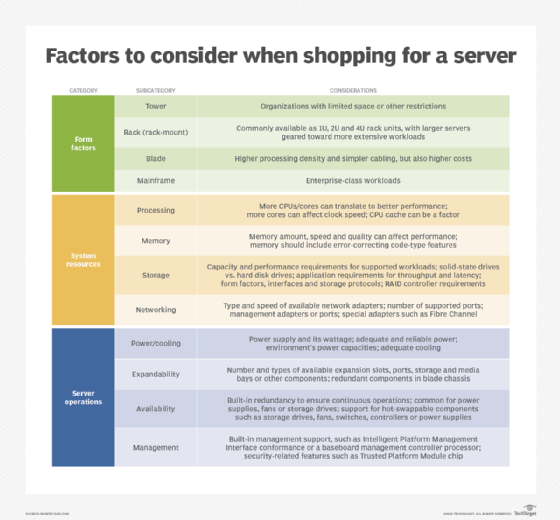

IT buyers in the server market must consider various factors when evaluating hardware vendor offerings, bearing in mind their current and future workload needs. An organization's requirements vary but revolve around the same server hardware features: CPU, memory, storage and connectivity.

CPU

The CPU is a fundamental component to review, given its role in running programs and manipulating data. Some servers run multiple processors, typically with one processor per socket. Others use a single processor consisting of multiple cores to support multiprocessing.

Buyers should consider the number of cores available on a processor, CPU clock speed, the available cache and the number of sockets. CPUs also offer varying performance levels, even if they have the same number of cores. Intel Xeon processors, for example, are categorized as Bronze, Silver, Gold and Platinum. These CPU classifications vary in terms of both price and performance.

Vendors offer a range of product options, so the IT buyer's job becomes finding the server hardware configuration that best fits a particular environment. Organizations running cloud infrastructure in a data center, for example, can perform a variety of general-purpose computing tasks on a 1 rack unit (1U) dual-CPU server or even a 0.5U single-CPU server. The relatively small 1U server might prove a good option since it can readily accommodate 16 cores with normal data center cooling approaches. This server category also provides some flexibility regarding storage drives and connections.

Memory

Server memory is critical for maximizing a system's performance. Memory modules differ in speed, with faster memory delivering better performance. More available memory enhances the workload performance as well. IT buyers should also consider server features that bolster reliability, such as fault-tolerant capabilities and error-correcting code.

Storage

A server's storage requirements depend on the intended applications and workloads. For example, a database server will have different needs than one running a web application. An IT buyer must examine server technology to ensure it meets the organization's storage requirements.

Most server vendors support flash storage through SSDs and traditional hard drive technology. Buyers should check with vendors to confirm the drive types and technologies they support, including Serial-Attached SCSI, Serial Advanced Technology Attachment and non-volatile memory express (NVMe). The intended server workload will determine which technology must be used. For instance, an organization dealing with large databases and unstructured data generally requires local instance drives, such as NVMe PCI Express units.

Other factors on the server storage checklist should include drive speeds and capacity, as well as the number of disks that can be striped together to exceed the capabilities of a single disk.

Connectivity

Network connectivity and interconnects -- such as host bus adapters, which link servers to storage -- are also important server considerations. Buyers should determine their connectivity requirements and then examine a server's specifications to meet those needs.

Variables to evaluate include the number and speed of Ethernet connectors, the number and type of USB ports, and support for storage systems, such as storage area networks. Consider the number of expansion slots included within a server, as they can be used to install expansion cards containing additional ports later.

Other features

Additional attributes to investigate include hot-swapping capabilities and the level of redundancy available for components such as hard drives, power supply units and fans. Server management capabilities and security features are also important.

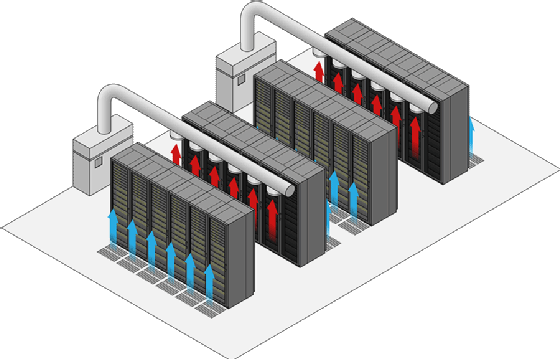

Admins should consider the general operating environment in which the new servers will reside. Keeping server temperature and humidity within recommended ranges contributes to high availability. In 2021, the American Society of Heating, Refrigerating and Air-Conditioning Engineers (ASHRAE) updated its recommended temperature and humidity ranges for data center hardware. The high end of the ASHRAE temperature range, for example, is now set at 80.6 degrees Fahrenheit. The guidelines can potentially help companies save on data center energy and electrical costs.

Management and maintenance

Managing servers and keeping them in working order encompasses a range of activities and tools.

Server monitoring systems, for example, provide critical data that admins can use to detect issues before they result in outages. Some of the essential components and tools of server monitoring include capacity planning and monitoring tools that track the usage of resources, such as CPU, memory and storage.

Specialized energy consumption tools enable admins to gauge a server's efficiency. Tools in this category include meters embedded in uninterruptible power supplies (UPSes), which report the power consumption of connected devices. Other options include external power meters, online energy consumption calculators and hardware vendors' configuration tools.

Although proper maintenance should extend server life, hardware degradation is inevitable. A server's physical components will eventually break down, with power, storage, CPU and memory among the problem areas. At some point, servers will need to be decommissioned and replaced.

Organizations should plan to decommission a server before it reaches its anticipated end of life. This involves inventorying the workloads running on the server and migrating them to new hardware or the cloud. After migrating the necessary data, organizations must destroy hard disks before recycling the server to mitigate data leakage.

Troubleshooting

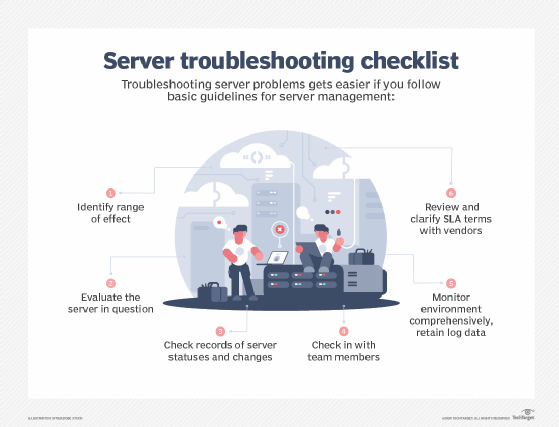

End-of-life hardware will eventually need replacing, but until then, admins must troubleshoot a server to keep it operating. An important first step is determining the scope of the problem: Who are the affected users, and are they reporting any consistent error messages? Once the problem is isolated to a particular server, admins can consult monitoring tools for alerts, check network connections and review the server environment's topology.

Troubleshooting and the use of monitoring tools can help organizations maintain system availability. The following are other steps organizations can take as they develop approaches to prevent and recover from server failure:

- Maintain adequate server ventilation.

- Keep the server's temperature within the manufacturer's recommendations.

- Follow a routine maintenance regimen.

Failure to update machines also ranks among the top common server hardware issues that can result in poor performance. Organizations should develop processes for these key areas:

- Regularly updating applications, firmware and OSes.

- Evaluating the server's security.

- Testing UPSes and generators.

Vendors and products

Customers can choose from myriad options when it's time to buy a new server. Server hardware options in the rack, blade and mainframe server market include offerings from over a dozen vendors. The following are some suppliers, listed in alphabetical order:

- Acer. Acer's server offerings include its Altos rack systems and tower servers.

- Asus. AsusTek Computer Inc. provides rack servers under the RS Series and ESC Series product lines. It also offers GPU, high-density, tower and edge servers.

- Cisco. Cisco aims to serve customers of varying sizes with its UCS B-Series Blade Servers, UCS C-Series rack servers, UCS S-Series storage servers and branch-office oriented Cisco UCS X-Series modular servers.

- Dell. Dell offers a wide range of rack and blade servers, including its PowerEdge R-Series rack servers, PowerEdge M-Series modular servers and PowerEdge T-Series tower servers.

- Fujitsu. Fujitsu's offerings for U.S. customers include its Primergy rack and modular servers and the more powerful Primequest series. The company also sells mainframe servers, but buyers must know that available models can vary between countries.

- Hewlett Packard Enterprise. HPE rack servers include the ProLiant DL Series. HPE also offers tower servers within its ML line.

- IBM. IBM launched the most recent version of its zSystem mainframes, z17, in 2025. Other offerings include a range of rack servers and the LinuxOne 5 system for running Linux on physical or virtual machines.

- Lenovo. Lenovo offers a variety of ThinkSystem rack and tower servers. The company also provides services for mission-critical workloads or supercomputing.

- Oracle. Oracle offers x86 servers and Sparc servers. The company's x86 servers scale from 16 cores to 192 cores. The Sparc server provides more power with up to 384 cores and 32 TB of RAM.

- Super Micro. Super Micro Computer Inc. provides rack systems for enterprise applications and in-memory computing. Other offerings include twin and blade servers.

Servers for small businesses

Small business customers tend to purchase tower servers. The following are a few examples of server hardware for small businesses, listed in alphabetical order:

- Asus. The company's TS100 machine can run as a workstation or server.

- Dell. The PowerEdge R360 is an entry-level server designed for SMB, near-edge computing and remote office environments.

- Fujitsu. The compact Primergy TX1310 M5 server features a screwless chassis and HDD quick-release capabilities.

- HPE. HPE's ProLiant ML350 Gen11 can be configured with various Xeon scalable processors.

- Lenovo. The ThinkSystem ST250 V3 is a small office server intended for business and branch office applications.

Purchasing considerations

Whether purchasing a server for an enterprise or a small business, the fundamentals are essentially the same: Understand your requirements and uses, then compare those to the products you evaluate.

Vendors offer various server form factors, configurations and models, many of which are optimized for particular workloads. Buyers should familiarize themselves with purchasing methods. Some vendors sell servers on their website through a direct sales force, while others use a combination of sales outlets that might require a sales representative.

Buyers must be willing to conduct a careful analysis or hire a consultant or channel partner, such as a value-added reseller, to identify the server type that best suits their needs. The following encompasses some of the essential purchasing considerations:

- Purchasing methods.

- OS licensing costs.

- Application licensing costs.

- Maintenance contract cost.

- Management software costs.

- Any costs associated with metered hardware usage.

- Expandability -- for example, can you add RAM, CPUs or expansion boards in the future?

- Which components are redundant?

- Are the redundant components hot-swappable?

- What are the power and cooling requirements?

- What remote management capabilities does the server support?

- What is the form factor, and how will it integrate with the existing infrastructure?

- What type of warranty does the vendor offer?

- Does the server support error-correcting memory and remote diagnostics?

- How many disks are supported, and of what type?

- What connectivity options exist?

- What is the manufacturer's reputation?

The future of server hardware

The future of server hardware must be viewed in the context of cloud computing and its growing influence. The cloud has become very popular among businesses. Small businesses and corporate data centers will continue to own and operate servers, often in hybrid cloud environments.

Servers will remain important, but how technology is consumed will continue to change, especially with the push toward green data centers and consumption-based pricing. Organizations and employees must be knowledgeable about the latest technology to advance in the future.

Editor's note: Vendors and products were chosen based on what companies have server hardware options and the likelihood a company, small or large, would use these servers. This list has been modified to show updated vendors that sell server hardware options as of 2025.

John Moore is a writer for Informa TechTarget covering the CIO role, economic trends and the IT services industry.

Brien Posey is a former 22-time Microsoft MVP and a commercial astronaut candidate. In his more than 30 years in IT, he has served as a lead network engineer for the U.S. Department of Defense and a network administrator for some of the largest insurance companies in America.